# iFPGA - Intermittent Intelligent FPGA Platform

Design Document

sdmay20-38

Client: Henry Duwe

Advisers: Henry Duwe

Team Members/Roles

Justin Sung - Embedded Systems Analyst

Zixuan Guo - Systems Diagram Expert

Jake Meiss - Electrical Engineer

Andrew Vogler - Hardware Applications Scientist

Jake Tener - Software Technician

Team Email: jsung7@iastate.edu

Team Website: http://sdmay2o-38.sd.ece.iastate.edu

# **Executive Summary**

# Development Standards & Practices Used

Hardware and software we will use in this project:

- Wifi harverst

- FPGA Circuit Board

- Microphone

- Voltage Booster

- Capacitor array

- Transmitter

#### **Engineering Standard**

- Honesty about the functionality and usefulness (#'s 3 & 6)

- Emphasis on Teamwork (#'s 7, 8, & 9)

- To make the highest quality product within our capability (#'s 5 & 6)

# **Summary of Requirements**

- Low Power

- Ability to checkpoint progress in a program

- Intermittent execution on an FPGA platform with frequent power cycling

# Applicable Courses from Iowa State University Curriculum

- CPRE488

- CPRE381

- EE330

- CPRE281

- CPRE288

# New Skills/Knowledge acquired that was not taught in courses

List all new skills/knowledge that your team acquired which was not part of your Iowa State curriculum in order to complete this project.

# **Table of Contents**

| ı Ir | itro             | luction                                            | 4  |

|------|------------------|----------------------------------------------------|----|

| 1    | .1               | Acknowledgement                                    | 4  |

| 1    | .2               | Problem and Project Statement                      | 4  |

| 1    | .3               | Operational Environment                            | 5  |

| 1    | .4               | Requirements                                       | 5  |

| 1    | .5               | Intended Users and Uses                            | 5  |

| 1    | .6               | Assumptions and Limitations                        | 5  |

| 1    | .7               | Expected End Product and Deliverables              | 6  |

| 2. 5 | Spec             | ifications and Analysis                            | 6  |

| 2    | 2.1              | Proposed Design                                    | 6  |

| 2    | 2.2              | Design Analysis                                    | 6  |

| 2    | 2.3              | Development Process                                | 6  |

| 2    | 2.4              | Design Plan                                        | 6  |

| 3. 5 | State            | ement of Work                                      | 6  |

| 3    | 3.1 P            | revious Work And Literature                        | 6  |

| 3    | 3.2 T            | echnology Considerations                           | 7  |

| 3    | 3.3 T            | ask Decomposition                                  | 7  |

| 3    | 3.4 P            | ossible Risks And Risk Management                  | 7  |

| 3    | 3.5 P            | roject Proposed Milestones and Evaluation Criteria | 7  |

| 3    | 3.6 P            | roject Tracking Procedures                         | 7  |

| 3    | 3.7 E            | xpected Results and Validation                     | 8  |

| 4. l | Proje            | ect Timeline, Estimated Resources, and Challenges  | 8  |

| 2    | 4.1 P            | roject Timeline                                    | 8  |

| 2    | 1.2 F            | easibility Assessment                              | 9  |

| 2    | 1.3 P            | ersonnel Effort Requirements                       | 9  |

| 2    | <sub>1.4</sub> ( | Other Resource Requirements                        | 9  |

| 2    | 1.5 F            | inancial Requirements                              | 9  |

| 5. 7 | Гesti            | ing and Implementation                             | 10 |

| 5    | 5.1              | Interface Specifications                           | 10 |

| 5    | 5.2              | Hardware and software                              | 10 |

|      | 5.3              | Functional Testing                                 | 10 |

|   | 5.4       | Non-Functional Testing | 10 |  |  |

|---|-----------|------------------------|----|--|--|

|   | 5.5       | Process                | 10 |  |  |

|   | 5.6       | Results                | 1  |  |  |

| 6 | . Closing | Closing Material       |    |  |  |

|   | 6.1 Con   | clusion                | 1  |  |  |

|   | 6.2 Refe  | 6.2 References         |    |  |  |

|   | 6.3 App   | pendices               | 1  |  |  |

List of figures/tables/symbols/definitions (This should be the similar to the project plan)

## 1 Introduction

#### 1.1 ACKNOWLEDGEMENT

Narayanan Vishak - Assisting in the design development.

Henry Duwe - Advised and set concrete goals for the team to work towards.

#### 1.2 PROBLEM AND PROJECT STATEMENT

Develop a hardware and software solution to intermittently execute a program targeted on a low power FPGA platform that can withstand multiple power cycling events.

As IoT applications become more prolific and integrated into society, the demand for more efficient and powerful devices grow. To address these demands, advancements in all aspects of embedded systems (e.g. memory space and speed, computational power, size, etc.) have become promising areas of study. Power consumption is one such area that has attracted a lot of attention recently. Reducing the power consumption of IoT devices results in longer device life, broaden IoT applicable areas, etc. . Thus, our project, iFPGA, attempts to study some pressing issues related to reducing power consumption.

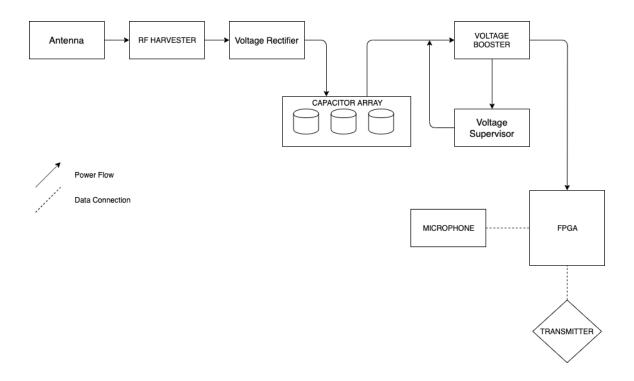

The iFPGA is a low power designed FPGA platform powered completely by a radio frequency harvester device to intermittently execute an audio recognition program with resilience against frequent power cycling events. If successful, the iFPGA prototype will uncover novel design solutions to address unreliable power sources, and broaden the feasible areas where IoT can be applied. The prototype will lead to more advanced designs that will build and improve upon any shortcomings of the final prototype. purely for research, the iFPGA will be applied to audio recognition.

#### 1.3 OPERATIONAL ENVIRONMENT

Since the iFPGA is purely a research based project, our prototype has no real-world application. It is purely to design a potential solution to address unreliable power sources.

#### 1.4 REQUIREMENTS

#### **Functional Requirement**

- Self energy harvesting

- Rectenna

- Data transmission

- 0 Bluetooth

- Program execution that can pause and continue while power toggling

- Non-volatile LUT

- Non-volatile memory

- Off-chip memory

#### **Non-Functional Requirements**

- Low Power

- Must be able to detect, perform computations, and transmit data at low power

- Distance of Transmissions

- Must be able to transmit data sufficient distances

- Sensor Range

- Sensor must be capable of capturing nearby audio

- Little to no human intervention after deployment

### 1.5 INTENDED USERS AND USES

This is the product designed for collecting and analyzing audio based data on an FPGA with an emphasis on low power design. It can be applicable to areas such as IoT and a prototype for developers to expand the study and project.

#### 1.6 ASSUMPTIONS AND LIMITATIONS

### Assumptions

Purely a feasibility project, no real world problem being addressed.

#### Limitations

- cost of prototype shall not exceed 200USD

- as low power as possible

#### 1.7 EXPECTED END PRODUCT AND DELIVERABLES

A prototype that can accelerate a portion of the audio recognition pipeline that demonstrates the ability to complete the program successfully with frequent power cycling events throughout its execution. Powered by a radio frequency harvester feeding into a capacitor array device. A demo to show these capabilities suffice in a successful end product.

Comprehensive documentation describing and explaining how to interface and justifying our design choices will be included with the end product prototype.

# 2. Specifications and Analysis

#### 2.1 PROPOSED DESIGN

- Market survey comparisons of potential components such as: FPGA, microphone, transceiver, etc.

- FPGA power simulations and computational power analysis

- Audio recognition software pipeline analysis to determine which step is most feasible on

- RF harvester, voltage booster, and capacitor array component analysis

#### 2.2 DESIGN ANALYSIS

Have not started designing.

### 2.3 DEVELOPMENT PROCESS

Agile sprints

#### 2.4 DESIGN PLAN

Deploy the platform in the field and be able to: (1) capture audio from its environment, (2) perform computation on the data, and (3) transmit the results from the computation to the main server.

# 3. Statement of Work

#### 3.1 PREVIOUS WORK AND LITERATURE

Paper that explains how to design an FPGA accelerated audio-related computational device.

https://ieeexplore.ieee.org/document/7763589

Market survey comparisons of components for the platform. Explained in previous sections in detail.

Self energy producing devices exists, but none that try to achieve something as costly, both in power and computational power, such as what iFPGA proposes. No other device in its class can sustain itself solely by radio frequency derived power while attempting costly cenergy and computations.

#### 3.2 TECHNOLOGY CONSIDERATIONS

Low power and budget are the two main factors that guided the technology choices made. Since the end product is a prototype to assess the feasibility of such a platform, the budget was restricted and considerations were made in light of it. The low power constraint also affected the technology choices.

#### 3.3 TASK DECOMPOSITION

- Decide on components that fit the project constraints and functional/non-functional requirements.

- 2. Design the hardware platform.

- 3. Design the software to handle the audio pipeline acceleration and intermittent programing.

- 4. Integrate (2) and (3).

### 3.4 POSSIBLE RISKS AND RISK MANAGEMENT

- Deeper knowledge of audio recognition pipeline

- Deeper knowledge of hardware/FPGa programming and development

- Graduation

### 3.5 PROJECT PROPOSED MILESTONES AND EVALUATION CRITERIA

**Key Milestones:**

- Component finalization list

- FPGA component integration

- Power analysis and component integration

- Intermittent programing design

- Completed hardware and software integration

#### 3.6 PROJECT TRACKING PROCEDURES

Weekly group meetings, weekly advisor meetings, and weekly work period meetings.

# 3.7 EXPECTED RESULTS AND VALIDATION

Deploy the platform in the field and be able to: (1) capture audio from its environment, (2) perform computation on the data, and (3) transmit the results from the computation to the main server. Frequent demonstrations will guarantee that each milestone is functioning as expected and that progress is being made in the right direction and in the right way.

# 4. Project Timeline, Estimated Resources, and Challenges

## 4.1 PROJECT TIMELINE

|                                                               | Sept 9-20 | Sept 21-Oct 21 | Oct 22-Nov | Nov 12-30 | Nov 31-Dec 20 | Jan 6 -<br>May |

|---------------------------------------------------------------|-----------|----------------|------------|-----------|---------------|----------------|

| Research<br>Requirements                                      |           |                |            |           |               |                |

| Simulate<br>Program &<br>Research<br>FPGA's                   |           |                |            |           |               |                |

| Understand<br>power levels &<br>build<br>electrical<br>design |           |                |            |           |               |                |

| Finalize diagram & Intended design blueprints                 |           |                |            |           |               |                |

| Build<br>individual<br>pieces, test,<br>and demo      |  |  |  |

|-------------------------------------------------------|--|--|--|

| Buy parts and<br>begin to mesh<br>project<br>together |  |  |  |

This schedule will keep our project on target while also allotting us enough time to sufficiently accomplish each important part. Our goal is to have each piece working well enough to be able to convince our client that we can build a working prototype during semester 2 by the end of semester 1.

### 4.2 FEASIBILITY ASSESSMENT

The project goals in themselves should be achievable. We will have a working battery-less FPGA that can perform some sort of computation. However, our current application is having it perform sound classification on the device. We have many worries about the power intensitivity of this, and think we will have to downgrade what the FPGA will do. We will spend some time analyzing this and re-evaluate often.

### 4.3 PERSONNEL EFFORT REQUIREMENTS

Our personal effort will be very high throughout the year. This has been deemed a difficult senior project by our advisor, so it will be tough for us. We will be spending a very high volume of time during the fourth cycle (Build individual pieces, test, and demo) as we get ready to show off our project ideas in order to begin prototyping.

#### 4.4 OTHER RESOURCE REQUIREMENTS

Our resources will be online material and software through the sites offering FPGA's. The hardware should be easily found at the university.

#### **4.5 FINANCIAL REQUIREMENTS**

The financial requirements for our project will not be great, most of the parts are very cheap.

# 5. Testing and Implementation

Testing is an extremely important component of most projects, whether it involves a circuit, a process, or a software library

Although the tooling is usually significantly different, the testing process is typically quite similar regardless of CprE, EE, or SE themed project:

- 1. Define the needed types of tests (unit testing for modules, integrity testing for interfaces, user-study for functional and non-functional requirements)

- 2. Define the individual items to be tested

- 3. Define, design, and develop the actual test cases

- 4. Determine the anticipated test results for each test case 5. Perform the actual tests

- 6. Evaluate the actual test results

- 7. Make the necessary changes to the product being tested 8. Perform any necessary retesting

- 9. Document the entire testing process and its results

Include Functional and Non-Functional Testing, Modeling and Simulations, challenges you've determined.

#### **5.1 INTERFACE SPECIFICATIONS**

- Discuss any hardware/software interfacing that you are working on for testing your project

#### **5.2** HARDWARE AND SOFTWARE

- Indicate any hardware and/or software used in the testing phase

- Provide brief, simple introductions for each to explain the usefulness of each

#### 5.3 FUNCTIONAL TESTING

Examples include unit, integration, system, acceptance testing

### 5.4 NON-FUNCTIONAL TESTING

Testing for performance, security, usability, compatibility

#### 5.5 PROCESS

- Explain how each method indicated in Section 2 was tested

- Flow diagram of the process if applicable (should be for most projects)

### 5.6 RESULTS

- List and explain any and all results obtained so far during the testing phase

- Include failures and successes

- Explain what you learned and how you are planning to change it as you progress with your project

- - If you are including figures, please include captions and cite it in the text

- This part will likely need to be refined in your 492 semester where the majority of the implementation and testing work will take place

- **-Modeling and Simulation**: This could be logic analyzation, waveform outputs, block testing. 3D model renders, modeling graphs.

- -List the **implementation Issues and Challenges**.

# 6. Closing Material

### 6.1 CONCLUSION

Summarize the work you have done so far. Briefly re-iterate your goals. Then, re-iterate the best plan of action (or solution) to achieving your goals and indicate why this surpasses all other possible solutions tested.

#### 6.2 REFERENCES

This will likely be different than in project plan, since these will be technical references versus related work / market survey references. Do professional citation style(ex. IEEE).

#### 6.3 APPENDICES

Any additional information that would be helpful to the evaluation of your design document.

If you have any large graphs, tables, or similar that does not directly pertain to the problem but helps support it, include that here. This would also be a good area to include hardware/software manuals used. May include CAD files, circuit schematics, layout etc. PCB testing issues etc. Software bugs etc.